You may contact the Digital Signal Processing Division in the following ways:

- By contacting your local Analog Devices Sales Representative

- For Marketing information, call (617) 461-3881 in Norwood, Massachusetts, USA

- For Applications Engineering information, call (617) 461-3672 in Norwood, Massachusetts, USA

- The Norwood office Fax number is (617) 461-3010

- The Norwood office may also be reached by

Telex: 924491

TWX: 710/394-6577

Cables: ANALOGNORWOODMASS

- The DSP Division runs a Bulletin Board Service that can be reached at 300, 1200, or 2400 baud, no parity, 8 bits data, 1 stop bit by dialing: (617) 461-4258

- By writing to:

Analog Devices DSP Division One Technology Way P.O. Box 9106 Norwood, MA 02062-9106 USA

### ADSP-2111 User's Manual

March 1990

© 1990 Analog Devices, Inc. ALL RIGHTS RESERVED

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use; nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under the patent rights of Analog Devices.

Printed in U.S.A.

First Edition

### Literature

#### **ADSP-2100 FAMILY MANUALS**

ADSP-2100 User's Manual/Architecture ADSP-2101 User's Manual/Architecture ADSP-2111 User's Manual/Architecture Complete descriptions of architecture and system interface.

ADSP-2100 Cross-Software Manual ADSP-2101 Cross-Software Manual Complete programmer's references, including optional C compiler.

ADSP-2100 Emulator Manual ADSP-2101 Emulator Manual ADSP-2101 EZ-ICE<sup>™</sup> Manual User's manuals for in-circuit Emulators.

**ADSP-2100A Evaluation Board Manual** A guide to the Evaluation Board including schematics for prototyping.

**ADSP-2101 EZ-LAB Manual** A guide to the EZ-LAB demonstration board and programs.

#### **APPLICATIONS INFORMATION**

**Digital Signal Processing Applications Using the ADSP-2100 Family.** (Formerly the *ADSP-2100 Family Applications Handbook, Volumes 1, 2 and 3.*) Topics include arithmetic, filters, FFTs, linear predictive coding, modem algorithms, graphics, pulse-code modulation, multirate filters, DTMF, multiprocessing, host interface and sonar.

#### SPECIFICATIONS INFORMATION

ADSP-2100A/ADSP-2100 Data Sheet ADSP-2101 Data Sheet ADSP-2111 Data Sheet (preliminary) ADSP-2105 Data Sheet (preliminary)

### Contents 🗖

#### **CHAPTER 1 INTRODUCTION**

| GENERAL DESCRIPTION                      | 1-1                                                                                                                                                                                         |

|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Architecture Overview                    |                                                                                                                                                                                             |

| Instruction Set                          |                                                                                                                                                                                             |

| INTERNAL ARCHITECTURE                    |                                                                                                                                                                                             |

| Computation Units                        |                                                                                                                                                                                             |

| Address Generators and Program Sequencer |                                                                                                                                                                                             |

| Timer                                    |                                                                                                                                                                                             |

| Host Interface Port                      |                                                                                                                                                                                             |

|                                          |                                                                                                                                                                                             |

| Buses                                    |                                                                                                                                                                                             |

| ADSP-2111 DEVELOPMENT SYSTEM             |                                                                                                                                                                                             |

| MANUAL ORGANIZATION                      |                                                                                                                                                                                             |

|                                          | Architecture Overview<br>Instruction Set<br>INTERNAL ARCHITECTURE<br>Computation Units<br>Address Generators and Program Sequencer<br>Timer<br>Host Interface Port<br>Serial Ports<br>Buses |

#### **CHAPTER 2 COMPUTATIONAL UNITS**

| 2.1   | ARITHMETIC ON THE ADSP-2111     |       |

|-------|---------------------------------|-------|

| 2.1.1 | Binary String                   | 2 – 1 |

| 2.1.2 | Unsigned                        | 2 – 1 |

| 2.1.3 | Signed Numbers: Twos-Complement | 2 – 1 |

| 2.1.4 | Fractional Representation: 1.15 | 2 – 1 |

| 2.1.5 | ALU Arithmetic                  |       |

| 2.1.6 | MAC Arithmetic                  | 2-2   |

| 2.1.7 | Shifter Arithmetic              |       |

| 2.1.8 | Summary                         | 2-3   |

| 2.2   | ARITHMETIC/LOGIC UNIT (ALU)     |       |

| 2.2.1 | ALU Block Diagram Discussion    | 2-4   |

| 2.2.2 | Standard Functions              | 2-6   |

| 2.2.3 | ALU Input/Output Registers      | 2 – 7 |

| 2.2.4 | Multiprecision Capability       |       |

iii

| 2.2.5   | ALU Saturation Mode2 – 7               |

|---------|----------------------------------------|

| 2.2.6   | ALU Overflow Latch Mode2 – 8           |

| 2.2.7   | Division                               |

| 2.2.8   | ALU Status                             |

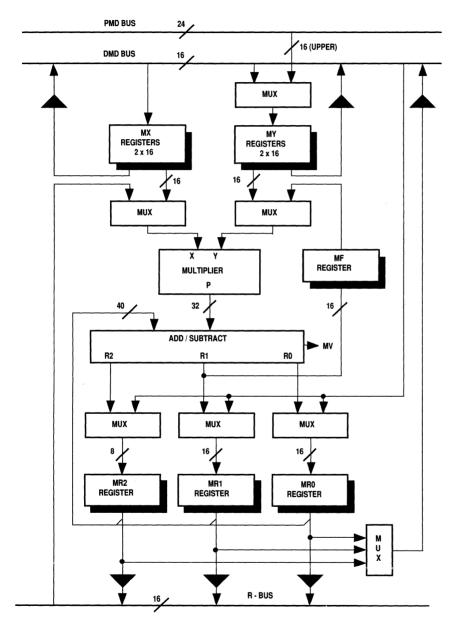

| 2.3     | MULTIPLIER/ACCUMULATOR (MAC)2 – 12     |

| 2.3.1   | MAC Block Diagram Discussion2 – 12     |

| 2.3.2   | MAC Operations                         |

| 2.3.2.1 | Standard Functions                     |

| 2.3.2.2 | Input Formats                          |

| 2.3.2.3 | MAC Input/Output Registers             |

| 2.3.2.4 | MR Register Operation2 – 17            |

| 2.3.2.5 | MAC Overflow and Saturation            |

| 2.3.2.6 | Rounding Mode2 – 18                    |

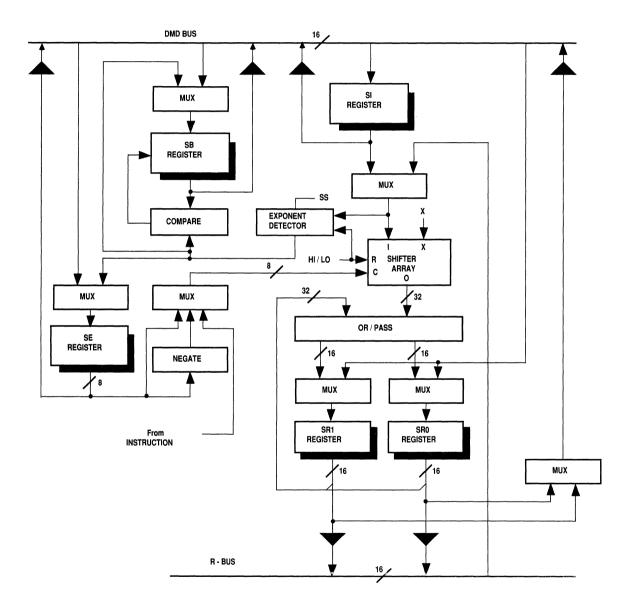

| 2.4     | BARREL SHIFTER                         |

| 2.4.1   | Shifter Block Diagram Discussion2 – 20 |

| 2.4.2   | Shifter Operations2 - 26               |

| 2.4.2.1 | Shifter Input/Output Registers         |

| 2.4.2.2 | Derive Block Exponent2 – 27            |

| 2.4.2.3 | Immediate Shifts2 – 28                 |

| 2.4.2.4 | Denormalize2 – 29                      |

| 2.4.2.5 | Normalize2 – 30                        |

|         |                                        |

#### CHAPTER 3 DATA MOVES

| 3.1     | INTRODUCTION                           | <br>.3 – 1 |

|---------|----------------------------------------|------------|

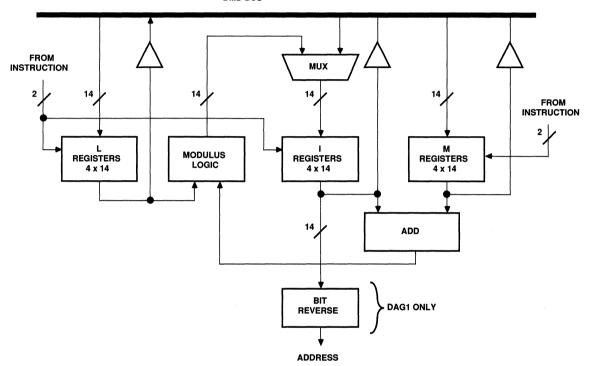

| 3.2     | DATA ADDRESS GENERATORS (DAGs)         |            |

| 3.2.1   | DAG Block Diagram Discussion           | <br>.3 – 1 |

| 3.2.2   | Modulo Addressing                      | <br>.3 – 3 |

| 3.2.3   | Calculating the Base Address           | <br>.3–4   |

| 3.2.3.1 | Circular Buffer Base Address Example 1 | .3 – 4     |

| 3.2.3.2 |                                        |            |

| 3.2.3.3 | Circular Buffer Operation Example 1    | <br>.3 – 4 |

| 3.2.3.4 | Circular Buffer Operation Example 2    | <br>.3 – 5 |

| 3.2.4   | Serial Ports                           | <br>.3 – 5 |

| 3.2.5   | Bit-Reverse Addressing                 | <br>.3 – 5 |

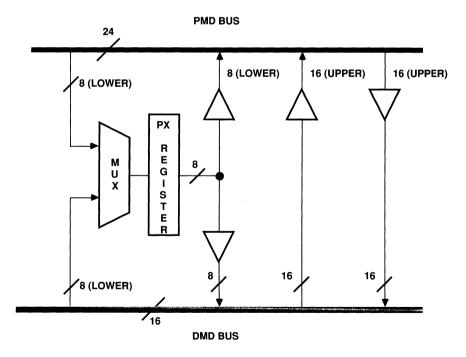

| 3.3     | PMD-DMD BUS EXCHANGE                   | <br>.3–6   |

| 3.3.1   | PMD-DMD Block Diagram Discussion       | <br>.3 – 6 |

#### CHAPTER 4 PROGRAM CONTROL

| 4.1     | INTRODUCTION                                 |

|---------|----------------------------------------------|

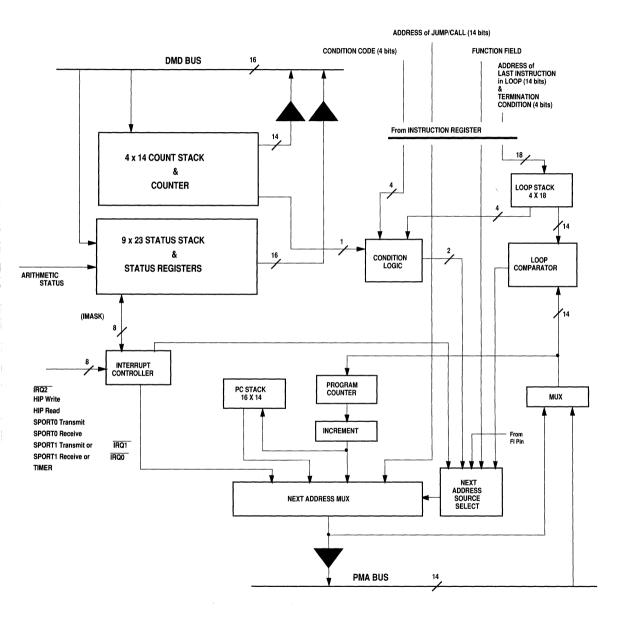

| 4.2     | PROGRAM SEQUENCER                            |

| 4.2.1   | Next Address Select Logic4 – 1               |

| 4.2.2   | Program Counter and Stack 4 – 3              |

| 4.2.3   | Down Counter and Stack4-4                    |

| 4.2.4   | Loop Comparator and Stack4 – 5               |

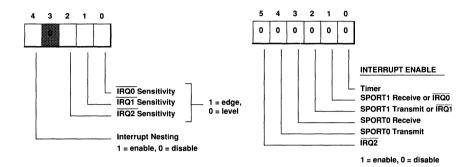

| 4.3     | INTERRUPT CONTROLLER                         |

| 4.3.1   | Configuring Interrupts4 – 9                  |

| 4.3.1.1 | Interrupt Control Register (ICNTL)4 – 10     |

| 4.3.1.2 | Interrupt Mask Register (IMASK)4 – 10        |

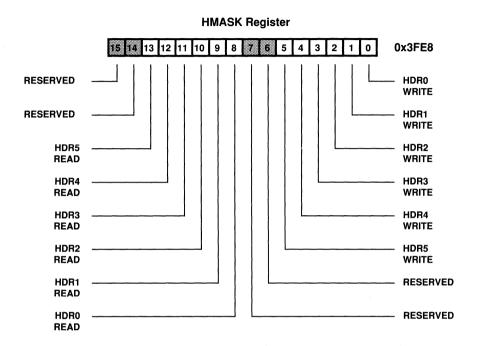

| 4.3.1.3 | HIP Interrupt Mask Register (HMASK)4 – 12    |

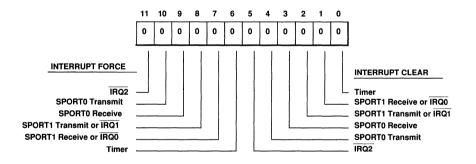

| 4.3.1.4 | Interrupt Force & Clear Register (IFC)4 – 12 |

| 4.3.2   | Interrupt Controller Operation4 – 13         |

| 4.4     | STATUS REGISTERS AND STACK                   |

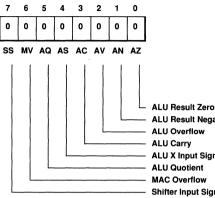

| 4.4.1   | Arithmetic Status Register (ASTAT)4 – 15     |

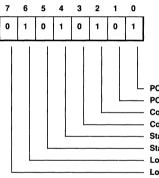

| 4.4.2   | Stack Status Register (SSTAT)4 – 16          |

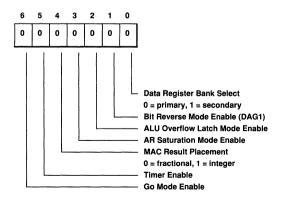

| 4.4.3   | Mode Status Register (MSTAT)4 – 17           |

| 4.5     | IDLE                                         |

| 4.6     | CONDITION LOGIC                              |

#### CHAPTER 5 TIMER

| 5.1 | OVERVIEW          | 5  | - 1 |

|-----|-------------------|----|-----|

| 5.2 | TIMER ARCHITECTUR | E5 | - 1 |

| 5.3 | RESOLUTION        | 5  | - 2 |

| 5.4 | EXAMPLE           | 5  | -2  |

| 5.5 | SUMMARY           | 5  | - 4 |

### **CHAPTER 6 HOST INTERFACE PORT**

| 6.1     | OVERVIEW                     | 6 – 1  |

|---------|------------------------------|--------|

| 6.2     | HIP PIN SUMMARY              |        |

| 6.3     | HIP FUNCTIONAL DESCRIPTION   |        |

| 6.4     | HIP OPERATION                |        |

| 6.4.1   | Polled Operation             |        |

| 6.4.1.1 | HIP Status Synchronization   |        |

| 6.4.2   | Interrupt-Driven Operation   | 6 – 10 |

| 6.4.3   | HDR Overwrite Mode           |        |

| 6.4.4   | Software Reset               |        |

| 6.5     | HIP INTERRUPTS               |        |

| 6.6     | HOST INTERFACE TIMING        |        |

| 6.7     | BOOT LOADING THROUGH THE HIP |        |

#### **CHAPTER 7 SERIAL PORTS**

| 7.1     | OVERVIEW                                      |        |

|---------|-----------------------------------------------|--------|

| 7.1.1   | Basic Features of SPORTS                      | 7 – 1  |

| 7.2     | SERIAL CLOCKS                                 |        |

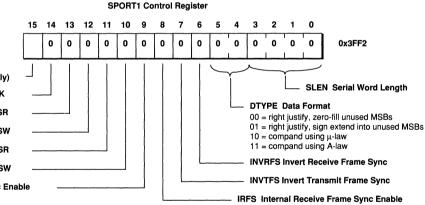

| 7.3     | FRAMING OPTIONS                               | 7 – 5  |

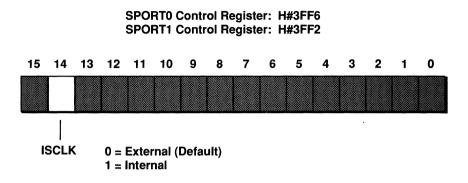

| 7.3.1   | Framing Synchronization: RFSR / TFSR          |        |

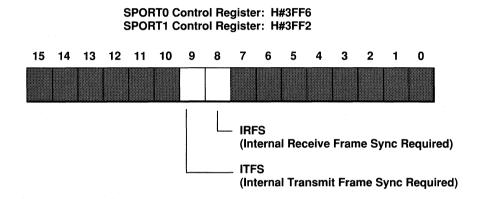

| 7.3.2   | External or Internal: IRFS / ITFS             | 7 – 6  |

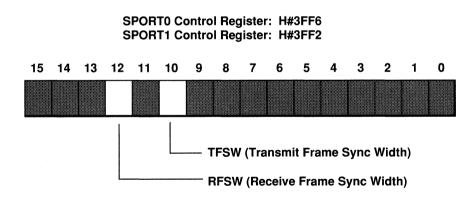

| 7.3.3   | Normal or Alternate Framing Mode: RFSW / TFSW | 7 – 7  |

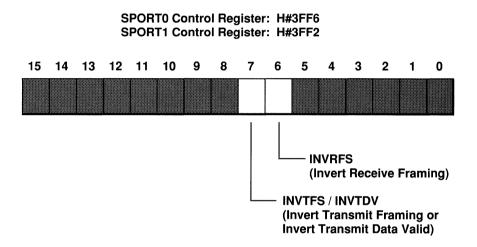

| 7.3.4   | Active High or Inverse Sense: INVRFS / INVTFS | 7 – 8  |

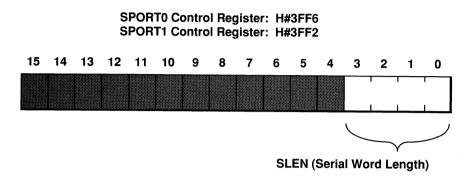

| 7.4     | SPORT WORD LENGTH: SLEN                       |        |

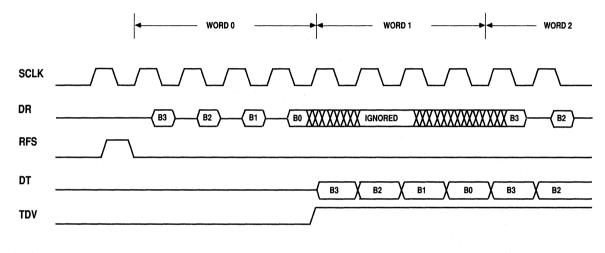

| 7.5     | WAVEFORM EXAMPLES                             |        |

| 7.6     | DATA REGISTERS & COMPANDING                   | 7 – 13 |

| 7.7.1   | Simple Operation Example                      | 7 – 14 |

| 7.7.2   | Companding & Data Format: DTYPE               | 7 – 14 |

| 7.7.2.1 | Companding Internal Data                      | 7 – 15 |

| 7.7.3   | Companding Operation Example                  | 7 – 15 |

| 7.7.4   | Contention For Companding Hardware            | 7 – 16 |

| 7.7     | INTERRUPTS & AUTOBUFFERING                    | 7 – 16 |

| 7.7.1   | Autobuffering Operation                       | 7 – 17 |

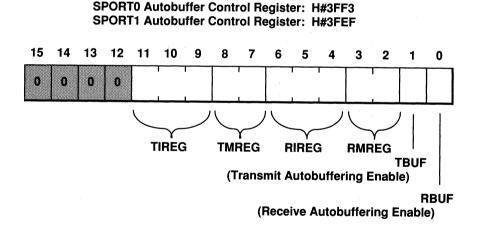

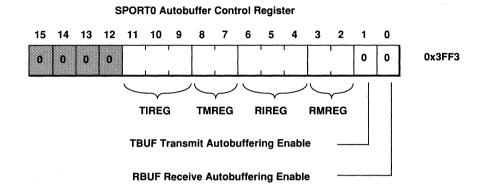

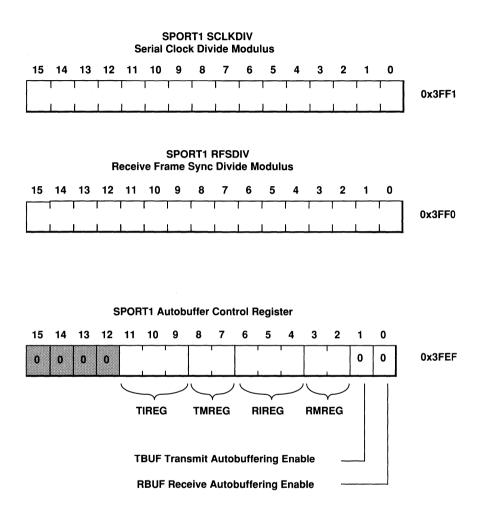

| 7.7.2   | Autobuffering Control Register                | 7 – 18 |

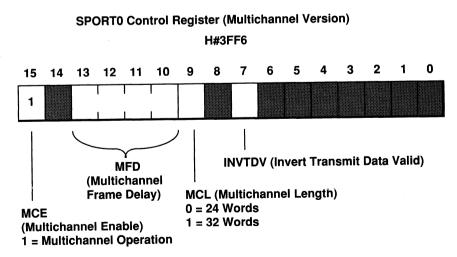

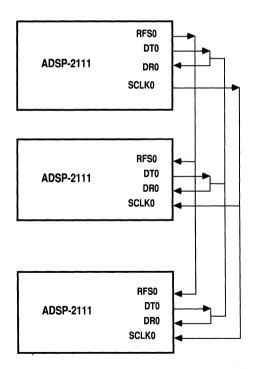

| 7.8   | MULTICHANNEL OPERATION         | 7 – 19 |

|-------|--------------------------------|--------|

| 7.8.1 | Multichannel Set Up            | 7 – 19 |

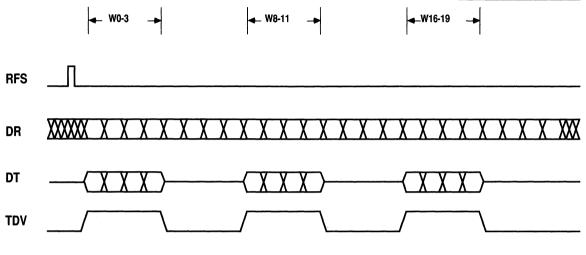

| 7.8.2 | Multichannel Operation         |        |

| 7.9   | SPORT ENABLE AND CONFIGURATION |        |

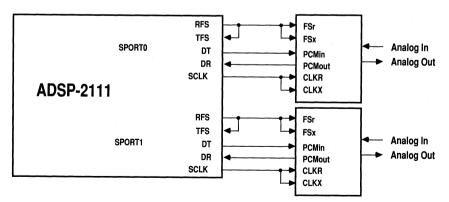

| 7.10  | SPORT HARDWARE INTERFACING     | 7 – 24 |

#### **CHAPTER 8 SYSTEM INTERFACE**

| INTRODUCTION    | 8-                                                                                        | - 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------------|-------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

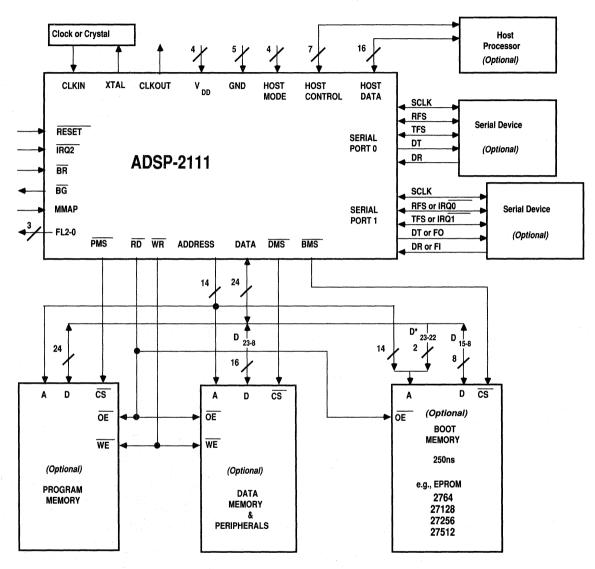

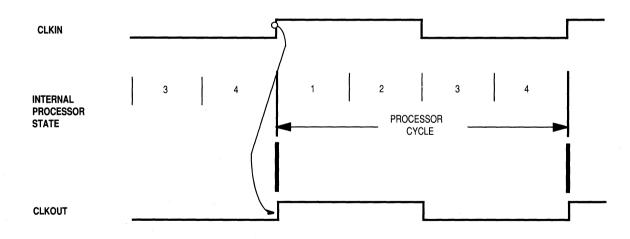

| CLOCK SIGNALS   | 8-                                                                                        | - 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Synchronization | Delay8 -                                                                                  | - 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                 |                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| RESET           |                                                                                           | - 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| INTERRUPTS      |                                                                                           | - 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Sensitivity     |                                                                                           | - 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| FLAGS           | 8 -                                                                                       | - 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                 | CLOCK SIGNALS<br>Synchronization<br>Clock Considera<br>RESET<br>INTERRUPTS<br>Sensitivity | CLOCK SIGNALS 8 - Synchronization Delay 8 - Clock Considerations 8 - Clock Considerations 8 - Clock Considerations 8 - RESET 8 |

#### **CHAPTER 9 MEMORY INTERFACE**

| INTRODUCTION                         |                                                                                                                                                                                                                                                                                                                                              |

|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

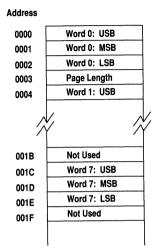

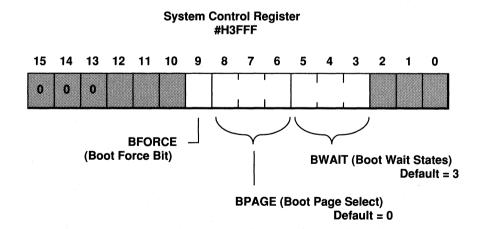

| BOOT MEMORY INTERFACE                |                                                                                                                                                                                                                                                                                                                                              |

| Boot Pages                           |                                                                                                                                                                                                                                                                                                                                              |

| Powerup Boot and Software Reboot     |                                                                                                                                                                                                                                                                                                                                              |

| Boot Memory Access                   |                                                                                                                                                                                                                                                                                                                                              |

| Boot Loading Sequence                |                                                                                                                                                                                                                                                                                                                                              |

| PROGRAM MEMORY INTERFACE             |                                                                                                                                                                                                                                                                                                                                              |

| Program Memory Read / Write          |                                                                                                                                                                                                                                                                                                                                              |

| Program Memory Map                   |                                                                                                                                                                                                                                                                                                                                              |

| DATA MEMORY INTERFACE                |                                                                                                                                                                                                                                                                                                                                              |

| Data Memory Read/Write               |                                                                                                                                                                                                                                                                                                                                              |

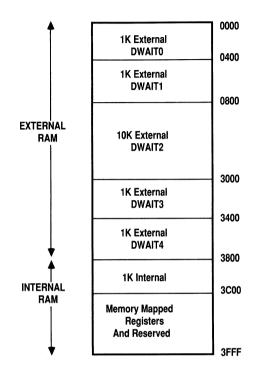

| Data Memory Map                      |                                                                                                                                                                                                                                                                                                                                              |

| Parallel & Memory-Mapped Peripherals |                                                                                                                                                                                                                                                                                                                                              |

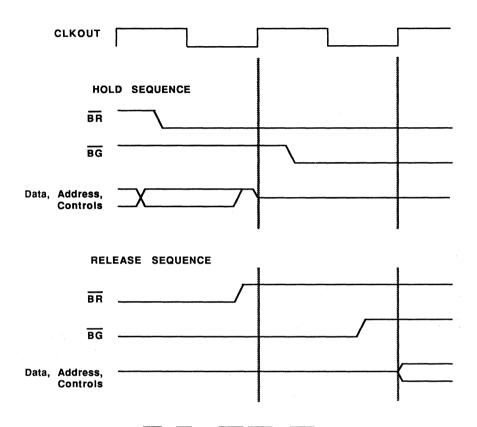

| BUS REQUEST / GRANT                  |                                                                                                                                                                                                                                                                                                                                              |

| MEMORY INTERFACE SUMMARY             |                                                                                                                                                                                                                                                                                                                                              |

|                                      | BOOT MEMORY INTERFACE<br>Boot Pages<br>Powerup Boot and Software Reboot<br>Boot Memory Access<br>Boot Loading Sequence<br>PROGRAM MEMORY INTERFACE<br>Program Memory Read / Write<br>Program Memory Map<br>DATA MEMORY INTERFACE<br>Data Memory Read/Write<br>Data Memory Map<br>Parallel & Memory-Mapped Peripherals<br>BUS REQUEST / GRANT |

#### **CHAPTER 10 INSTRUCTION SET OVERVIIEW**

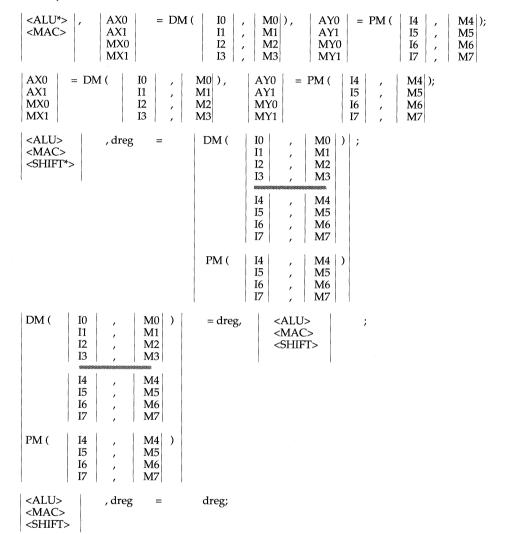

| 10.1 INTRODUCTION                                    |          |

|------------------------------------------------------|----------|

| 10.2 INSTRUCTION TYPES                               |          |

| 10.2.1 Multifunction Instructions                    |          |

| 10.2.1.1 ALU/MAC with Data & Program Memory Read     | d 10 – 4 |

| 10.2.1.2 Data & Program Memory Read                  |          |

| 10.2.1.3 Computation With Memory Read                |          |

| 10.2.1.4 Computation With Memory Write               |          |

| 10.2.1.5 Computation With Data Register Move         |          |

| 10.2.2 ALU, MAC and Shifter Instructions             |          |

| 10.2.2.1 ALU Group                                   |          |

| 10.2.2.2 MAC Group                                   |          |

| 10.2.2.3 Shifter Group                               | 10 – 11  |

| 10.2.3 MOVE: Read & Write                            |          |

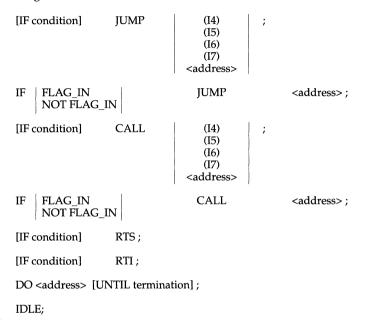

| 10.2.4 Program Flow Control                          |          |

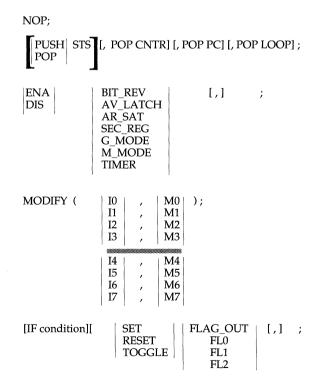

| 10.2.5 Miscellaneous Instructions                    |          |

| 10.3 DATA STRUCTURES                                 | 10 – 17  |

| 10.3.1 Arrays                                        |          |

| 10.3.2 Circular Arrays/Buffers                       |          |

| 10.3.3 Ports & Memory-Mapping                        |          |

| 10.4 PROGRAM EXAMPLE                                 |          |

| 10.4.1 Example Program: Setup Routine Discussion     |          |

| 10.4.2 Example Program: Interrupt Routine Discussion |          |

#### APPENDIX A INSTRUCTION CODING

| A.1 | OPCODES             | A –  | 1 |

|-----|---------------------|------|---|

| A.2 | ABBREVIATION CODING | GA – | 6 |

#### APPENDIX B DIVISION EXCEPTIONS

| B.1   | DIVISION FUNDAMENTALS | B–1   |

|-------|-----------------------|-------|

| B.1.1 | Signed Division       | B – 1 |

| B.1.2 | Unsigned Division     | B-2   |

| B.1.3 | Output Formats        |       |

| B.1.4 | Integer Division      | B – 3 |

| B.2   | ERROR SITUATIONS        | В- | - 3 |

|-------|-------------------------|----|-----|

| B.2.1 | Negative Divisor Error  | Β- | - 3 |

| B.2.2 | Unsigned Division Error | В- | - 4 |

|       | SOFTWARE SOLUTION       |    |     |

#### APPENDIX C PIN INFORMATION

| C.1 | PIN DESCRIPTION | C – 1 |

|-----|-----------------|-------|

| C.2 |                 | C-2   |

#### APPENDIX D CONTROL/STATUS REGISTERS

#### FIGURES

| 1.1 | ADSP-2111 Internal Arc        | hitecture 1 - 5  |

|-----|-------------------------------|------------------|

| 2.1 | ALU Block Diagram             | 2-5              |

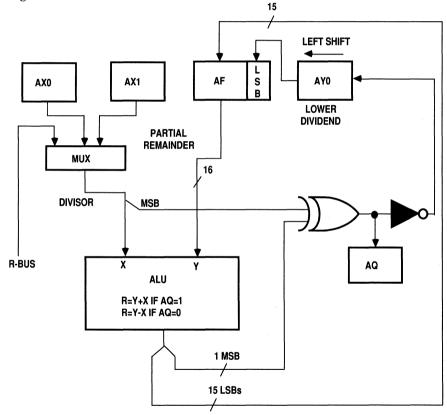

| 2.2 | <b>DIVS Operation Block D</b> | iagram2 – 9      |

| 2.3 | DIVQ Operation Block D        | biagram          |

| 2.4 | Quotient Format               |                  |

| 2.5 | MAC Block Diagram             |                  |

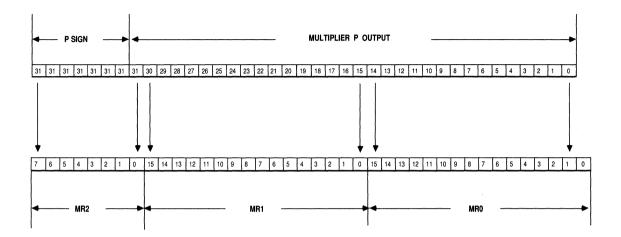

| 2.6 | Fractional Multiplier Res     | ult Format2 – 16 |

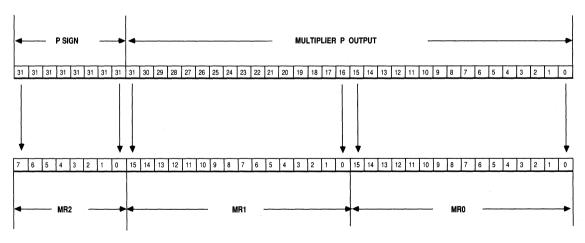

| 2.7 |                               | Format2 – 16     |

| 2.8 | Shifter Block Diagram         | 2-21             |

| 3.1 | Data Address Generator        | Block Diagram    |

| 3.2 | PMD-DMD Bus Exchan            | ge3-7            |

| 4.1 | Program Sequencer Blo         | ck Diagram       |

| 4.2 |                               |                  |

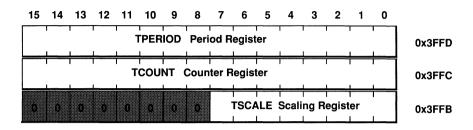

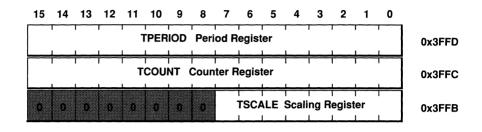

| 5.1 | Timer Begisters               |                  |

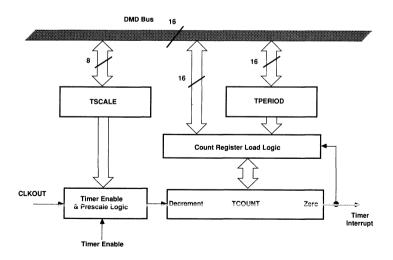

| 5.2 | •                             |                  |

|     | •                             |                  |

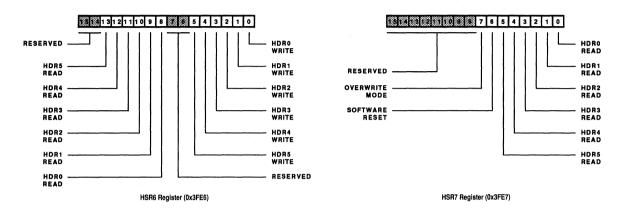

| <ul> <li>6.2 HIP Status Registers</li> <li>6.3 Host Status Synchronization</li> <li>6.4 ADSP-2111 Status Synchronization</li> </ul> |          |

|-------------------------------------------------------------------------------------------------------------------------------------|----------|

|                                                                                                                                     | Q        |

| 6.4 ADSP-2111 Status Synchronization                                                                                                | - 0      |

|                                                                                                                                     | - 9      |

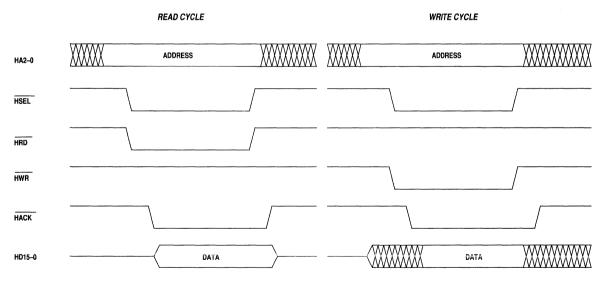

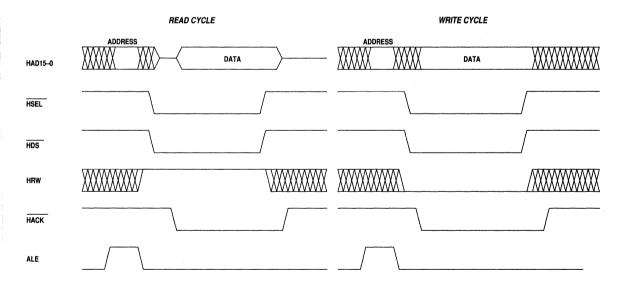

| 6.5 HIP Timing: Separate Strobes, Separate Buses                                                                                    | 13       |

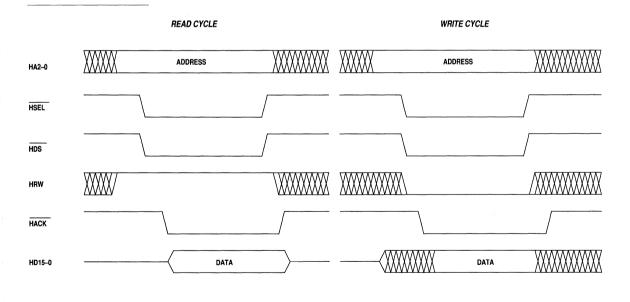

| 6.6 HIP Timing: Multiplexed R/W Strobe, Separate Buses                                                                              | 14       |

| 6.7 HIP Timing: Separate Strobes, Multiplexed Buses                                                                                 |          |

| 6.8 HIP Timing: Multiplexed R/W Strobe, Multiplexed Buses                                                                           |          |

|                                                                                                                                     |          |

| 7.1 Serial Port Block Diagram7                                                                                                      |          |

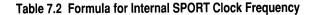

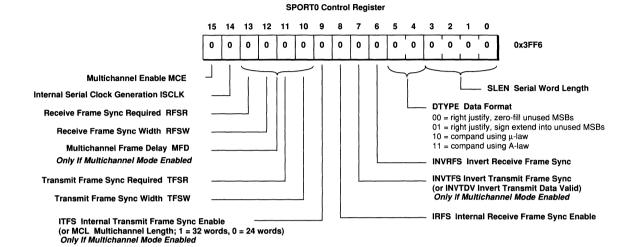

| 7.2 ISCLK Bit in SPORT Control Register                                                                                             |          |

| 7.3 Framing Required Bits in SPORT Control Register                                                                                 | - 5      |

| 7.4 Internal Framing Bits in SPORT Control Register7                                                                                | - 6      |

| 7.5 Framing Width Bits in SPORT Control Register                                                                                    | -7       |

| 7.6 Active High/Low Bits in SPORT Control Register7                                                                                 | - 8      |

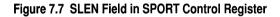

| 7.7 SLEN Field in SPORT Control Register7                                                                                           | - 9      |

| 7.8 SPORT Receive, Normal Framing (Internal & External Shown)7                                                                      | - 9      |

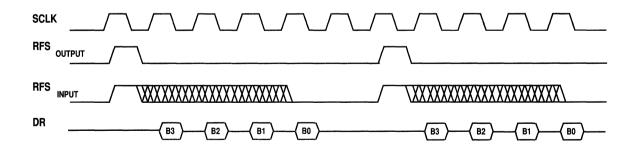

| 7.9 SPORT Continuous Receive, Normal Framing (Internal & External)                                                                  | 10       |

| 7.10 SPORT Receive, Alternate Framing (Internal & External Shown)                                                                   | 10       |

| 7.11 SPORT Continuous Receive, Alternate Framing (Internal & External)7 -                                                           | 10       |

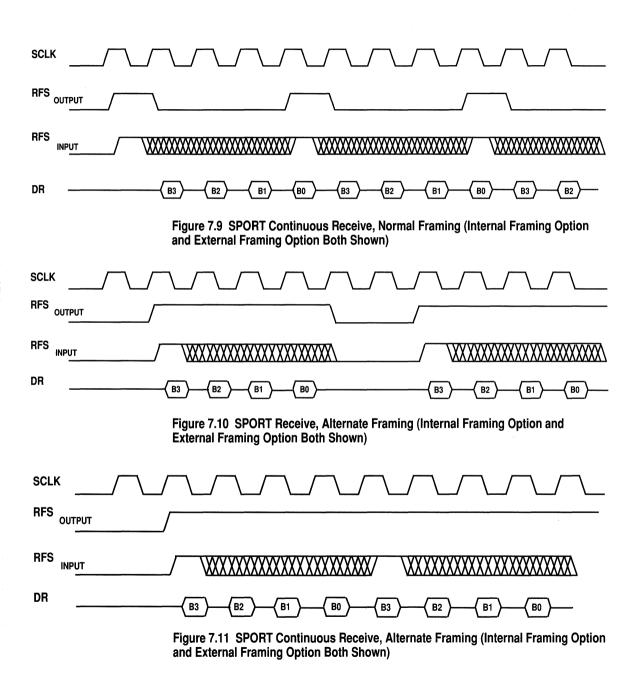

| 7.12 SPORT Start Frameless Receive, Normal Framing                                                                                  | 11       |

| 7.13 SPORT Start Frameless Receive, Alternate Framing                                                                               | 11       |

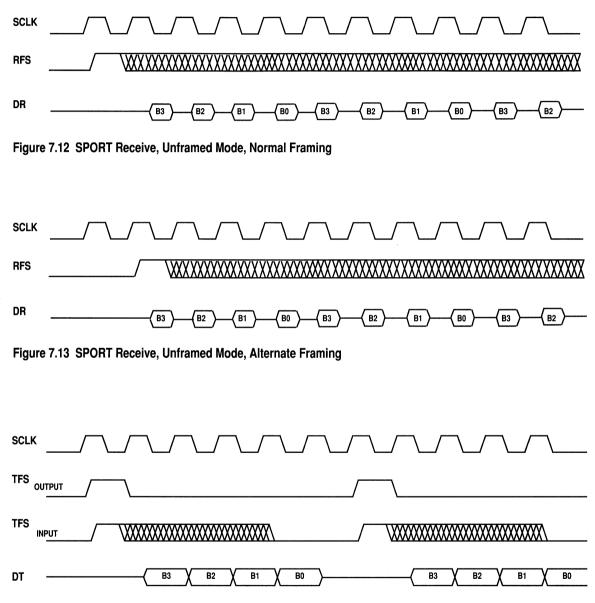

| 7.14 SPORT Transmit, Normal Framing (Internal & External Shown)                                                                     | 11       |

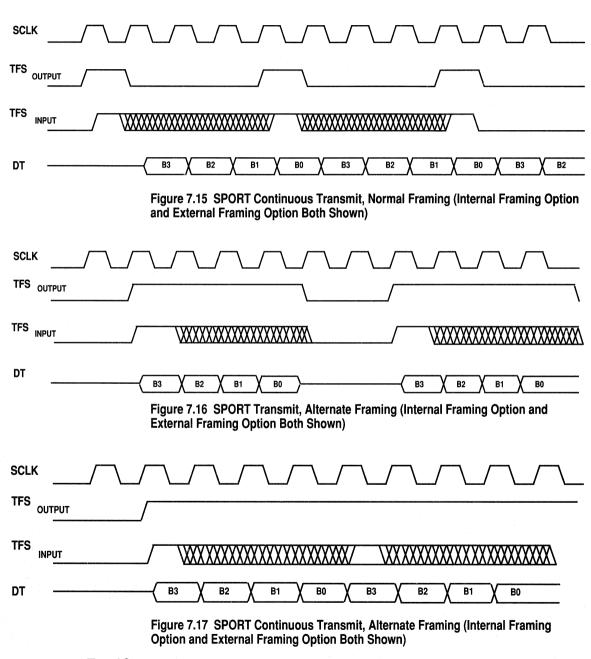

| 7.15 SPORT Continuous Transmit, Normal Framing (Internal & External)7 -                                                             | 12       |

| 7.16 SPORT Transmit, Alternate Framing (Internal & External Shown)                                                                  | 12       |

| 7.17 SPORT Continuous Transmit, Alternate Framing (Internal & External)7 -                                                          |          |

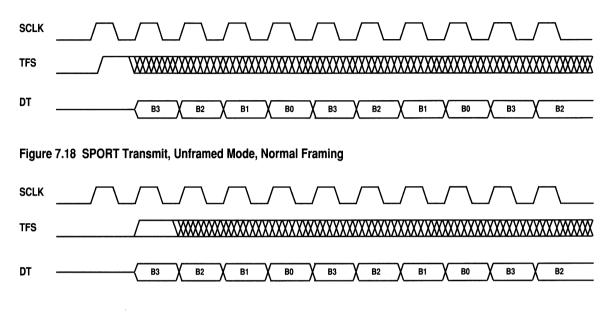

| 7.18 SPORT Start Frameless Transmit, Normal Framing                                                                                 |          |

| 7.19 SPORT Start Frameless Transmit, Alternate Framing                                                                              |          |

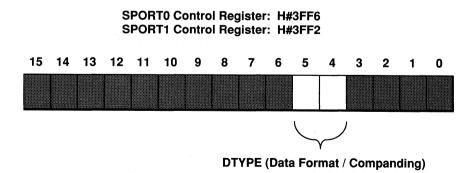

| 7.20 DTYPE Field in SPORT Control Register                                                                                          | 14       |

| 7.21 SPORT Autobuffer Control Register                                                                                              | 18       |

| 7.22 SPORT0 Control Register (Multichannel Version)                                                                                 |          |

| 7.23 SPORT Multichannel Frame Delay Examples                                                                                        | 20       |

| 7.24 SPORT0 Multichannel Word Enable Registers                                                                                      |          |

| 7.25 Start of Multichannel Operation                                                                                                |          |

| 7.26 Complete Multichannel Example                                                                                                  |          |

|                                                                                                                                     |          |

|                                                                                                                                     | <u> </u> |

|                                                                                                                                     |          |

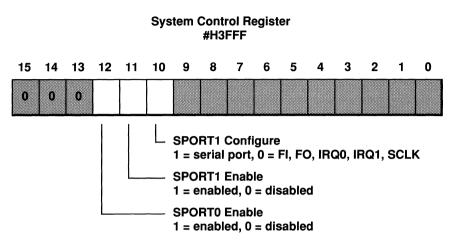

| 7.27 SPORT Enables in System Control Register7 –                                                                                    | 24       |

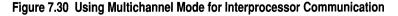

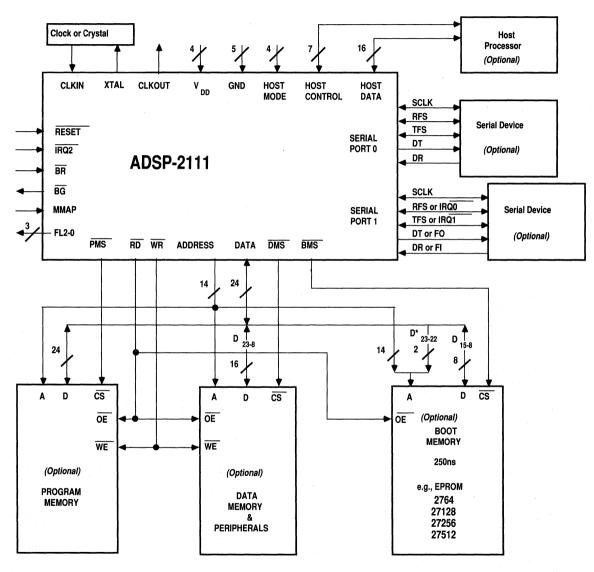

| 8.1  | ADSP-2111 Basic System                                           |         |

|------|------------------------------------------------------------------|---------|

| 8.2  | Clock or Crystal Configuration                                   |         |

| 8.3  | Clock Signals & Processor States                                 |         |

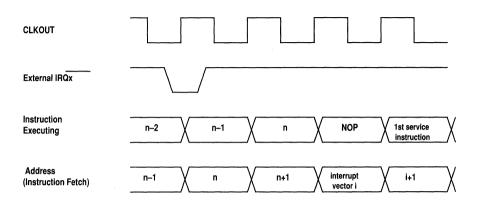

| 8.4  | Interrupt Service Timing                                         |         |

| 9.1  | ADSP-2111 System Block Diagram                                   | 9 – 2   |

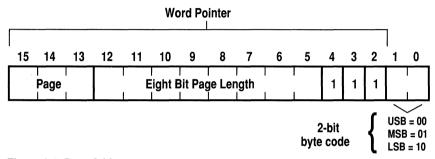

| 9.2  | EPROM Contents                                                   |         |

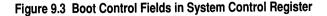

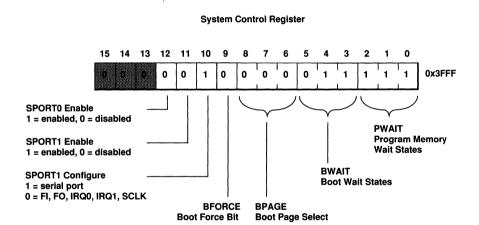

| 9.3  | Boot Control Fields in System Control Register                   | 9-4     |

| 9.4  | Boot Address                                                     | 9 – 6   |

| 9.5  | Boot Loading Order                                               | 9 – 7   |

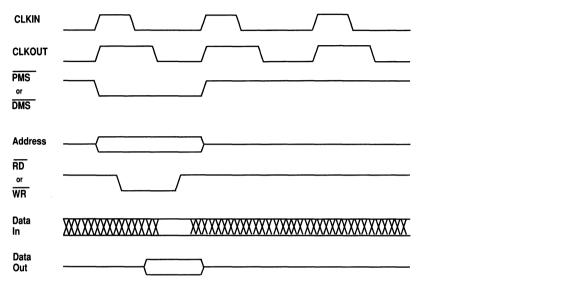

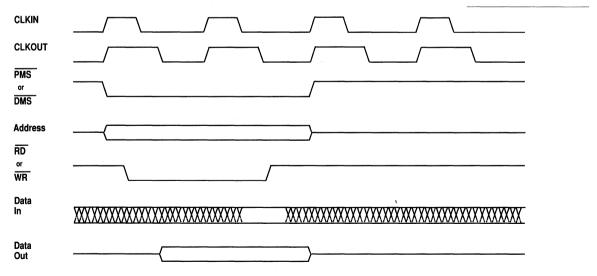

| 9.6a | Program & Data Memory Read & Write Operations, No Wait States    | 9 – 8   |

| 9.6b | Program & Data Memory Read & Write Operations, One Wait States . | 9 – 9   |

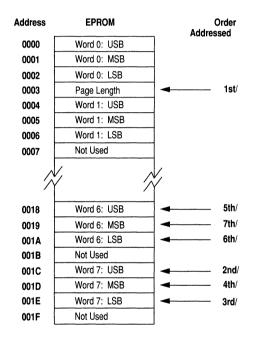

| 9.7  | Program Memory Wait State Field In System Control Register       | 9 – 9   |

| 9.8  | Program Memory Configurations                                    | 9 – 10  |

| 9.9  | Data Memory Wait State Control Register                          | 9 – 12  |

| 9.10 | Data Memory Configuration                                        |         |

| 9.11 | Bus Hold / Release                                               | 9 – 15  |

| 10.1 | Program Example Listing 1, Main Routine & Constants File         | 10 – 21 |

| 10.2 | Program Example Listing 2, Interrupt Routine                     | 10 – 23 |

| B.1  | Listing B.1: Division Error Routine                              | B – 6/8 |

#### TABLES

| 2.1<br>2.2<br>2.3<br>2.4 | Arithmetic Formats Used by the ADSP-2111<br>ALU Saturation Mode<br>MAC Saturation Instruction Effect<br>Shifter Array Characteristic               | 2 – 7<br>2 – 18 |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| 2.5                      | Shifter Exponent Detector Characteristic                                                                                                           |                 |

| 4.1<br>4.2<br>4.3<br>4.4 | DO UNTIL Termination Condition Logic<br>Interrupts & Interrupt Vector Addresses<br>IMASK Entering Interrupt Service Routines<br>IF Condition Logic | 4 – 8<br>4 – 11 |

| 5.1<br>5.2               | Timer Range & Resolution<br>Example of Timer Operation                                                                                             |                 |

| 6.1  | Host Interface Port Pins                                     | 6 – 2   |

|------|--------------------------------------------------------------|---------|

| 6.2  | HIP Configuration Modes                                      | 6 – 3   |

| 7.1  | SPORT External Signals and Pins                              |         |

| 7.2  | Formula for Internal SPORT Clock Frequency                   | 7 – 3   |

| 7.3  | Common SPORT Frequencies (Internally-Generated)              | 7 – 4   |

| 7.4  | DTYPE Field Values                                           |         |

| 7.5  | SPORT Interrupt Priorities                                   | 7 – 16  |

| 8.1  | ADSP-2111 State After RESET or Software Reboot               | 8 – 6   |

| 9.1  | Program Memory Restart / Interrupt Vectors                   |         |

| 9.2  | Pin States During Memory Access                              |         |

| 9.3  | Pin States During Reset, Booting and Bus Grant               | 9 – 16  |

| 10.1 | Summary of Valid Combinations For Multifunction Instructions | 10 – 7  |

| 10.2 | Multifunction Instructions                                   |         |

| 10.3 | ALU Instructions                                             |         |

| 10.4 | MAC Instructions                                             |         |

| 10.5 | Shifter Instructions                                         |         |

| 10.6 | ADSP-2111 Register Set: reg & dreg                           |         |

| 10.7 | MOVE Instructions                                            |         |

| 10.8 | Program Flow Control Instructions                            |         |

| 10.9 | Miscellaneous Instructions                                   | 10 – 16 |

### 1.1 GENERAL DESCRIPTION

The ADSP-2111 is a programmable single-chip microcomputer optimized for digital signal processing (DSP) and other high-speed numeric processing applications. Digital signal processing demands high performance. But high performance cannot be measured by speed alone. What distinguishes DSPs from other types of microprocessor and microcontroller architectures is how well they perform in each of the following areas.

• Fast and flexible arithmetic

The ADSP-2111 provides single-cycle computation for multiplication, multiplication with accumulation, arbitrary amounts of shifting, and standard arithmetic and logical operations. In addition, the arithmetic units allow for any sequence of computation so that a given DSP algorithm can be executed without being reformulated.

• Extended dynamic range on multiplication/accumulation

Extended sums-of-products, common in DSP algorithms, are supported by the ADSP-2111. Its 40-bit accumulator provides protection against overflow in successive accumulations to ensure that no loss of data or range occurs. Special instructions are also provided for implementing block floating-point scaling of data.

• Single-cycle fetch of two operands (from either on- or off-chip)

In extended sums-of-products calculations, two operands are always needed to feed the calculation. The ADSP-2111 is able to sustain twooperand data throughput.

• Hardware circular buffers (both on- and off-chip)

A large class of DSP algorithms, including most filters, requires circular buffers. The ADSP-2111 provides hardware to handle address pointer

wraparound, reducing overhead (thereby increasing performance) and simplifying implementation.

Zero-overhead looping and branching

DSP algorithms are repetitive and most logically expressed as loops. The ADSP-2111 program sequencer supports looped code with zero overhead, combining excellent performance with the clearest program structure. Likewise, there are no overhead penalties for conditional program flow on the ADSP-2111.

#### 1.1.1 Architecture Overview

Like the ADSP-2100 microprocessor, the ADSP-2111 contains three fullfunction and independent computation units: an arithmetic/logic unit, a multiplier/accumulator and a barrel shifter. The computation units process 16-bit data directly and provide for multiprecision computation.

Two dedicated address generators and a powerful program sequencer supply addresses for on-chip or external memory access. The sequencer supports single-cycle conditional branching and executes program loops with zero overhead. Dual data address generators allow the processor to output simultaneous addresses for dual operand fetches. Together the sequencer and data address generators allow computational operations to execute with maximum efficiency.

On chip, the ADSP-2111 uses a modified Harvard architecture in which data memory stores data and program memory stores both instructions and data. The processor can fetch an operand from on-chip data memory, an operand from on-chip program memory and the next instruction from on-chip program memory in a single cycle. (The speed of on-board memory access makes this possible and eliminates the need for cache memory as on the ADSP-2100.) This scheme is extended off-chip via a single external memory address bus and data bus which may be used for either program or data memory access and for booting. Consequently, the processor can access external memory once in any cycle.

In addition to the address and data bus for external memory connection, the ADSP-2111 has a Host Interface Port (HIP) for direct connection (requiring no glue logic) to a host processor. The HIP is made up of 16 data pins and 11 control pins. The HIP is extremely flexible and has provisions to allow simple interface to a variety of host processors. For example, the Motorola 68000, the Intel 8051 and the Analog Devices' ADSP-2101 can be easily connected to the HIP.

Boot circuitry provides for loading on-chip program memory automatically after reset with automatic wait state generation for interfacing to a single low-cost EPROM. Multiple programs can be selected and loaded from the EPROM with no additional hardware.

The HIP provides a second method of booting. The host processor provides opcodes to the ADSP-2111 HIP, and the ADSP-2111 automatically transfers the data, in this case an opcode or part of an opcode, directly into internal program memory.

The memory interface supports memory-mapped peripherals with programmable wait state generation. External devices can gain control of buses with bus request/grant signals ( $\overline{BR}$  and  $\overline{BG}$ ). An optional execution mode allows the ADSP-2111 to continue running while the buses are granted to another master as long as an external memory operation is not required.

The ADSP-2111 can respond to eight user interrupts. There can be up to three external interrupts, configured as edge- or level-sensitive. Internal interrupts can be generated from the timer, the host interface port (HIP) and the serial ports (SPORTs).

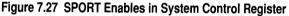

The two serial ports provide a complete serial interface with hardware companding (data compression and expansion). Both  $\mu$ -law and A-law companding are supported. The ports interface easily and directly to a wide variety of popular serial devices. Each port can generate an internal programmable clock or accept an external clock.

As a result of its architecture, the ADSP-2111 exhibits a high degree of parallelism, tailored to DSP requirements. In a single cycle, the ADSP-2111 can:

- generate the next program address

- fetch the next instruction

- perform one or two data moves

- update one or two data address pointers

- perform a computation

- receive and/or transmit data via the two serial ports

- receive and/or transmit data via the host interface port.

#### 1.1.1 Instruction Set

The instruction set is an upwardly-compatible superset of the ADSP-2100 instruction set. Chapter 10, "Instruction Set Overview" highlights the capabilities of the ADSP-2111 instruction set and shows an example program.

The ADSP-2111 instruction set provides flexible data moves and multifunction (one or more data moves with computation) instructions. Every instruction can be executed in a single processor cycle. The ADSP-2111 assembly language uses an algebraic syntax for ease of coding and readability. A comprehensive set of development tools supports program development.

#### 1.2 INTERNAL ARCHITECTURE

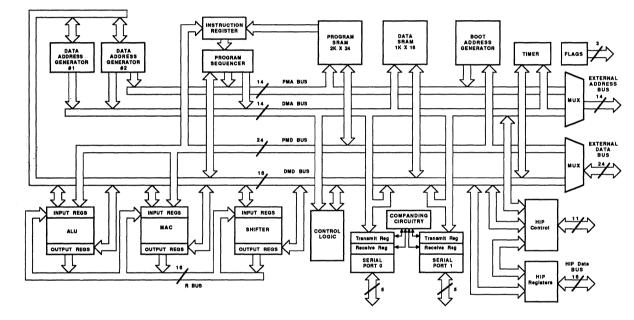

This section gives an overview of the ADSP-2111 internal architecture based on Figure 1.1. Each component is described in detail in the following chapters.

#### Component

Chapter / Section

| • | Arithmetic/logic unit       | 2.2 |

|---|-----------------------------|-----|

|   | Multiplier/accumulator      | 2.3 |

| ٠ | BarreÎ shifter              | 2.4 |

| ٠ | Two data address generators | 3.2 |

| ٠ | PMD-DMD bus exchange        | 3.3 |

| ٠ | Program sequencer           | 4.2 |

| ٠ | Status registers and stacks | 4.4 |

| ٠ | Timer                       | 5   |

| ٠ | Host interface port         | 6   |

| ٠ | Serial ports                | 7   |

|   |                             |     |

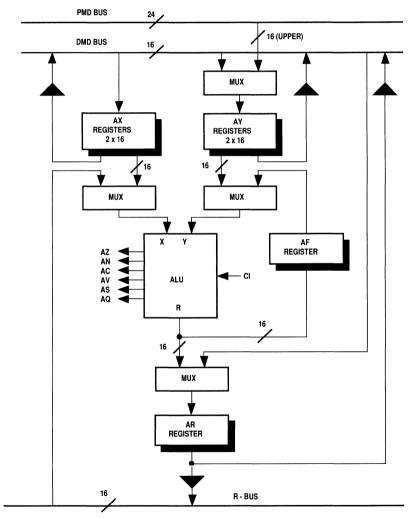

#### **1.2.1** Computation Units

The ADSP-2111 contains three full-function and independent computation units: an arithmetic/logic unit (ALU), a multiplier/accumulator (MAC) and a barrel shifter. The computation units process 16-bit data directly and provide for multiprecision computation.

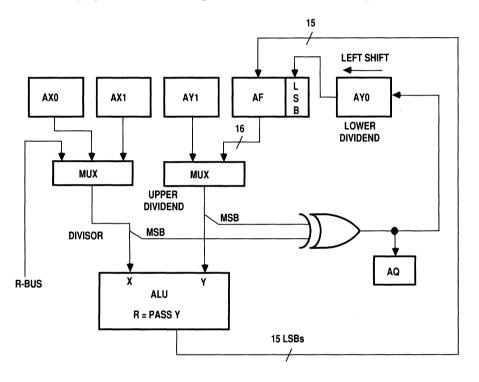

The ALU performs a standard set of arithmetic and logic operations in addition to division primitives. The MAC performs single-cycle multiply, multiply/add and multiply/subtract operations. The shifter performs logical and arithmetic shifts, normalization, denormalization, and derive

exponent operations. The shifter implements numeric format control including multiword floating point representations. The computational units are arranged side-by-side instead of serially so that the output of any unit may be the input of any unit on the next cycle. The internal result (R) bus directly connects the computational units to make this possible.

Figure 1.1 ADSP-2111 Internal Architecture

All three sections contain input and output registers which are accessible from the internal data memory data (DMD) bus. Computational operations generally take their operands from input registers and load the result into an output register. The registers act as a stopover point for data between memory and the computational circuitry. This feature introduces one level of pipelining on input, and one level on output. The R bus allows the result of a previous computation to be used directly as the input to another computation. This avoids excessive pipeline delays when a series of different operations are performed.

#### 1.2.2 Address Generators and Program Sequencer

Two dedicated data address generators and a powerful program sequencer ensure efficient use of these computational units. The data address generators (DAGs) provide memory addresses when memory data is transferred to or from the input/output registers. Each DAG keeps track of up to four address pointers. When a pointer is used for indirect addressing, it is post-modified by a value in a specified register. With two independent DAGs, the processor can generate two addresses simultaneously for dual operand fetches.

A length value may be associated with each pointer to implement automatic modulo addressing for circular buffers. (The circular buffer feature is also used by the serial ports for automatic data transfers. Refer to the chapter on serial ports for additional information.) DAG1 can supply addresses to data memory only. DAG2 can supply addresses to either the data memory or the program memory. Two independent address generators allow for simultaneous access of data stored in the program memory and data stored in the data memory.

The program sequencer supplies instruction addresses to the program memory. The sequencer is driven by the instruction register which holds the currently executing instruction. The instruction register introduces a single level of pipelining into the program flow. Instructions are fetched and loaded into the instruction register during one processor cycle, and executed during the following cycle while the next instruction is prefetched. To minimize overhead cycles, the sequencer supports conditional jumps, subroutine calls and returns in a single-cycle. With an internal loop counter and loop stack, the ADSP-2111 executes looped code with zero-overhead. No explicit jump instructions are required to loop.

#### 1.2.3 Timer

The programmable interval timer provides periodic interrupt generation. An 8-bit prescaler register allows the timer to decrement a 16-bit count register over a range from each cycle to every 256 cycles. An interrupt is generated when this count register reaches zero. The count register is automatically reloaded from a 16-bit period register and the count resumes immediately.

#### 1.2.4 Host Interface Port

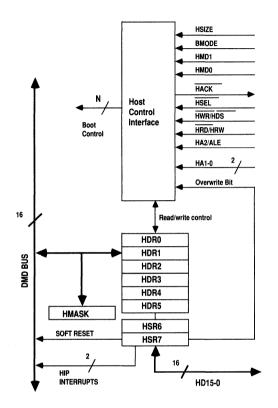

The host interface port (HIP) is a parallel I/O port that allows for an easy connection to a host processor. Through the HIP, the ADSP-2111 can be used as a memory-mapped peripheral to a host computer. The HIP

operates in parallel with and asynchronous to the ADSP-2111 processing core. The host interface port consists of registers through which the ADSP-2111 and the host computer pass data and status information. The HIP can be configured for: an 8-bit data bus or 16-bit data bus; a multiplexed address/data bus or separate address and data buses; and separate read and write strobes or a read/write strobe and a data strobe.

#### 1.2.5 Serial Ports

The ADSP-2111 has two bidirectional double-buffered serial ports (SPORTs) for serial communications. The SPORTs are synchronous and use framing signals to control data flow. Each SPORT can generate its serial clock internally or use an external clock. The framing sync signals may be generated internally or by an external device. Word lengths may vary from three to sixteen bits. One SPORT (SPORT0) has a multichannel capability which allows the receiving or transmitting of arbitrary data words from a 24-word or 32-word bitstream. SPORT1 may optionally be configured as two additional external interrupt pins and the Flag Out (FO) and Flag In (FI) pins.

#### 1.2.6 Buses

The internal components are supported by five internal buses: The PMA and DMA buses are used internally for the addresses associated with program and data memory. The program memory data (PMD) and data memory data (DMD) buses are used for the data associated with the memory spaces. These two pairs of buses are multiplexed off chip to the external address and data buses. The BMS, DMS and PMS signals select the different address spaces. The R bus is an internal bus which serves to transfer intermediate results directly between the various computational sections.

The program memory address (PMA) bus is 14 bits wide allowing direct access of up to 16K words of mixed instruction code and data. The program memory data (PMD) is 24 bits wide to accommodate the 24-bit instruction width.

The data memory address (DMA) bus is 14 bits wide allowing direct access of up to 16 K words of data. The data memory data (DMD) bus is 16 bits wide. The data memory data (DMD) bus provides a path for the contents of any register in the processor to be transferred to any other register or to any external data memory location in a single cycle. The data memory address comes from two sources: an absolute value specified in the instruction code (direct addressing) or the output of a data address

generator (indirect addressing). Only indirect addressing is supported for data fetches from program memory.

The program memory data (PMD) bus can also be used to transfer data to and from the computational units through direct paths or via the PMD-DMD bus exchange unit The PMD-DMD bus exchange unit permits data to be passed from one bus to the other. It contains hardware to overcome the 8-bit width discrepancy between the two buses, if necessary.

#### 1.3 ADSP-2111 DEVELOPMENT SYSTEM

The ADSP-2111 is supported with a complete set of software and hardware development tools. The ADSP-2111 Development System includes the Cross-Software Development System for software design and an Emulator for hardware debugging.

The Cross-Software Development System includes:

System Builder

The System Builder defines the architecture of systems under development. This includes the specification of the amount of external RAM/ROM memory available and any memory-mapped I/O ports for the target hardware environment as well as the allocation of program and data memory.

Assembler

The Assembler assembles the source code and data modules as well as supporting the high-level syntax of the instruction set. In addition to supporting a full range of system diagnostics, the Assembler provides flexible macro processing, include files, and modular code development.

Linker

The Linker links separately assembled modules. It maps the linked code and data output to the target system hardware, as specified by the System Builder output.

Simulator

The Simulator performs an interactive, instruction-level simulation of the hardware configuration described by the System Builder. It flags illegal operations and supports full symbolic assembly and disassembly.

• PROM Splitter

This module reads the Linker output and generates PROM burner compatible files.

• C Compiler

The C Compiler reads ANSI (Draft Standard) C source and outputs ADSP-2111 source code ready to be assembled. It also supports inline assembler code.

• In-circuit Emulator

The Emulator provides hardware debugging of the ADSP-2111 systems with stand-alone in-circuit emulation, using an ADSP-2111 in selfemulation mode. The Emulator design provides execution with little or no degradation in processor performance.

For additional information on the Development System, refer to the *ADSP-2111 Cross-Software Manual*.

#### 1.4 MANUAL ORGANIZATION

The *ADSP-2111 User's Manual* provides the necessary information to understand and evaluate the operation of the ADSP-2111. Together with the *ADSP-2111 Data Sheet*, this manual provides all the information required to design a ADSP-2111 hardware system. For information on programming the chip, refer to the *ADSP-2111 Cross-Software Manual*.

The rest of this manual is organized as follows.

Chapter 2, "Computational Units," describes the internal architecture and function of the three computational units of the ADSP-2111: the arithmetic/logic unit, the multiplier/accumulator and the barrel shifter.

Chapter 3, "Data Moves," describes the data address generators (DAGs) and the PMD-DMD Bus Exchange Unit.

Chapter 4, "Program Control," describes the program sequencer, interrupt controller and status and condition logic.

Chapter 5, "Timer," explains the programmable interval timer.

Chapter 6, "Host Interface Port" describes the operation of the host interface port, including boot loading through the host interface port and software reset.

Chapter 7, "Serial Ports," describes the two ADSP-2111 serial ports: SPORT0 and SPORT1.

Chapter 8 "System Interface," provides a description of the control interface of the ADSP-2111. Information on the software reboot function is also included.

Chapter 9, "Memory Interface," describes the three memory spaces on the ADSP-2111: data memory, program memory and boot memory. For timing characteristics, refer to the *ADSP-2111 Data Sheet*.

Chapter 10, "Instruction Set Overview," is an overview of the ADSP-2111 instruction set. All instructions are grouped by major type. Detailed programmer's reference material is in the *ADSP-2111 Cross-Software Manual*; this chapter gives enough information to understand the capabilities and flexibility of the instruction set.

Appendix A, "Instruction Coding," shows the complete set of opcodes and provides the bit patterns for the choices within each field of the instruction word.

Appendix B, "Division Exceptions," describes signed and unsigned division.

Appendix C, "Pin Information," describes the pin functions and pin configurations of the ADSP-2111.

Appendix D, "Control/Status Registers," summarizes the contents and locations of all control and status registers in the ADSP-2111.

### 2.1 ARITHMETIC ON THE ADSP-2111

This chapter describes the architecture and function of the three computational units of the ADSP-2111: the arithmetic/logic unit, the multiplier/accumulator and the barrel shifter.

To better understand the detailed discussion of these units you should first understand how the ADSP-2111 handles binary arithmetic. The ADSP-2111 is a 16-bit, fixed-point machine. Special features support multiword arithmetic and block floating point. Most operations assume a twos-complement number while others assume an unsigned number or a simple binary string. This section discusses the arithmetic used by each computational unit or operation.

#### 2.1.1 Binary String

This is the simplest binary notation; sixteen bits are treated as a bit pattern. Examples of computation using this format are the logical operations: NOT, AND, OR, XOR. These ALU operations treat their operands as binary strings with no provision for sign bit or binary point placement.

#### 2.1.2 Unsigned

Unsigned binary numbers may be thought of as positive, having nearly twice the magnitude of a signed number of the same length. The least significant words of multiple precision numbers are treated as unsigned numbers.

#### 2.1.3 Signed Numbers: Twos-Complement

In discussions of ADSP-2111 arithmetic "signed" refers to twos-complement. Most ADSP-2111 operations presume or support twos-complement arithmetic. The ADSP-2111 does not use signedmagnitude, ones-complement, BCD or excess-n formats.

#### 2.1.4 Fractional Representation: 1.15

The ADSP-2111 is optimized for arithmetic values in a fractional binary format denoted by 1.15 ("one dot fifteen"). (Referred to in some contexts as 16.15 or Q15.) This is a fixed-point format. Used with the MSB as a sign

bit, the 1.15 means one sign bit and fifteen fractional bits representing values from –1 up to one LSB less than +1.

#### 2.1.5 ALU Arithmetic

All operations on the ALU treat operands and results as simple 16-bit binary strings, except the signed division primitive (DIVS). Various status bits treat the results as signed: the overflow (AV) condition code, and the negative (AN) flag.

The logic of the overflow bit (AV) is based on twos-complement. It is set if the MSB changes in a manner not predicted by the signs of the operands and the nature of the operation. For example, adding two positive numbers must generate a positive result; a change in the sign bit signifies an overflow and sets AV. Adding a negative and a positive may result in either a negative or positive result, but cannot overflow.

The logic of the carry bit (AC) is based on unsigned-magnitude. It is set if a carry is generated from bit 16 (the MSB). The (AC) bit is most useful for the lower word portions of a multiword operation.

#### 2.1.6 MAC Arithmetic

The multiplier produces results that are binary strings. The inputs are "interpreted" according to the information given in the instruction itself (signed times signed, unsigned times unsigned, a mixture or round). The 32-bit result from the multiplier is assumed to be signed, in that it is sign-extended across the full 40-bit width of the MR register set.

The ADSP-2111 supports two modes of format adjustment: the fractional mode for fractional operands, 1.15 format (1 signed bit, 15 fractional bits), and the integer mode for integer operands, 16.0 format. When multiplying 1.15 operands, the result is 2.30 (30 fractional bits). To correct this, in the fractional mode, a left shift occurs between the multiplier product (P) and the multiplier result register (MR). This shift (1 bit to the left) causes the multiplier result to be 1.31 which can be rounded to 1.15. Figure 2.6, in the MAC section of this chapter, shows this.

In the integer mode, the left shift does not occur. For example, if the operands are in the 16.0 format, the 32-bit multiplier result would be in 32.0. A left shift would change the numerical representation. Figure 2.7 in the MAC section of this chapter shows this.

#### 2.1.7 Shifter Arithmetic

Many operations in the Shifter are explicitly geared to signed (twos-

complement) or unsigned values: Logical Shifts assume unsignedmagnitude or binary string values and Arithmetic Shifts assume twoscomplement.

The exponent logic assumes twos-complement numbers. The exponent logic supports block floating point, which is also based on twoscomplement fractions.

#### 2.1.8 Summary

The table below summarizes some of the arithmetic characteristics of the ADSP-2111 computational operations. In addition to the numeric types described in this section, the ADSP-2111 C Compiler supports a form of 32-bit floating-point in which one 16-bit word is the exponent and the other word is the mantissa. See the ADSP-2111 Cross-Software Manual.

| Operation                                                                                                                                | Arithmetic Formats                                                                                                                                  |                                                                                                                                        |

|------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| ALU                                                                                                                                      | Operands                                                                                                                                            | Result                                                                                                                                 |